Bayesian machine learning to optimize 2-D material field-effect transistors

Leuven | More than two weeks ago

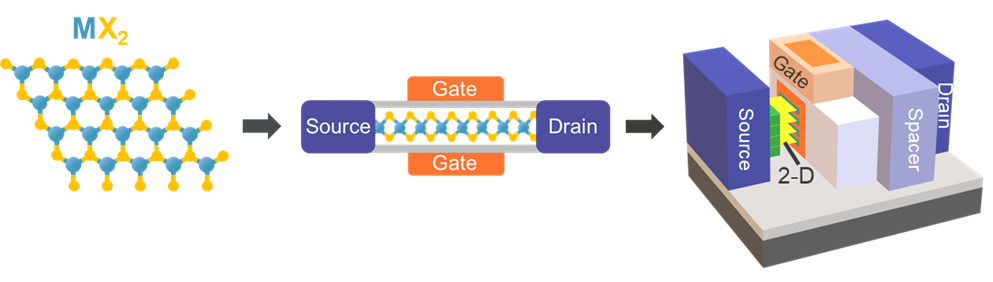

Two-dimensional (2-D) materials are a promising class of semiconductor channel materials for future field-effect transistors (FETs) to continue transistor scaling into the next decade and beyond [1]. They are envisioned to replace or complement silicon in advanced technology nodes. Popular research materials include MoS2 and WS2, but the space of possible chemical compositions is much larger. These materials are particularly suited for vertical 3-D transistor architectures with nanosheet channels, such as the complementary FET (CFET), as they allow for sub-nanometer sheet thickness, while maintaining good carrier mobility. This enables further gate length scaling and reduces the cell parasitics by making the transistor stack less tall.

The optimization space of possible 3-D architectures is huge, and it is even larger considering the choice of 2-D material. Many design parameters affect performance across various levels of abstraction, linking choices on the material level to the device and circuit level. Currently, research on 2-D FETs is carried out largely with manual simulations or small-scale optimization algorithms, which is inefficient for device-technology co-optimization.

Bayesian machine learning is an optimization approach for goal functions that are poorly known and/or costly to evaluate. It relies on sampling to update knowledge about the optimization landscape, which allows to find global optima. It has been successfully utilized in various fields, ranging from particle physics to drug development, but its use in semiconductor device research is so far limited [2].

Hence, the goal of this PhD is to implement a Bayesian optimization methodology for 2-D material FETs. The project will start by setting up a simple optimization flow at the device level, which can optimize a structure for device level metrics. The input of this flow will be device simulations using TCAD tools and modeling software available in the research team. Next, the flow will be expanded to encompass other levels of abstraction. Depending on the interests of the PhD candidate, the focus can be either toward the circuit or toward the material level. In the former, the link is made to cell-level parasitics extraction and circuit level metrics. In the latter, the flow is linked to ab-initio computed material parameters.

For this ambitious PhD project, imec and the University of Texas at Dallas are soliciting enthusiastic PhD candidates for a dual PhD degree. In the first 2 years of this PhD project, you will work at the UT Dallas while the last 2 years will be at imec Belgium. You will gain international experience in two top research teams in the field of exploratory logic devices. You will work in world-class research environments, with close contact to market-leading industrial partners. Since 2-D materials are currently on the roadmap to replace silicon in future technology nodes, this research has the potential to drive the shape of transistors that will be in devices that people worldwide use every day. The project requires a strong background in semiconductor device modeling and electrical engineering, with good programming skills being a significant asset.

[1] D. Verreck et al., "The Promise of 2-D Materials for Scaled Digital and Analog Applications," IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2023, pp. 26-28.

[2] P. -J. Chuang, et al., "Algorithmic Optimization of Transistors Applied to Silicon LDMOS," IEEE Access, vol. 11, pp. 64160-64169, 2023.

Required background: Semiconductor device modeling, nanoelectronics, computer science, materials science

Type of work: 60% modeling and implementation, 25% design, 15% literature

Supervisor: Anne Verhulst

Daily advisor: Devin Verreck

The reference code for this position is 2025-048. Mention this reference code on your application form.