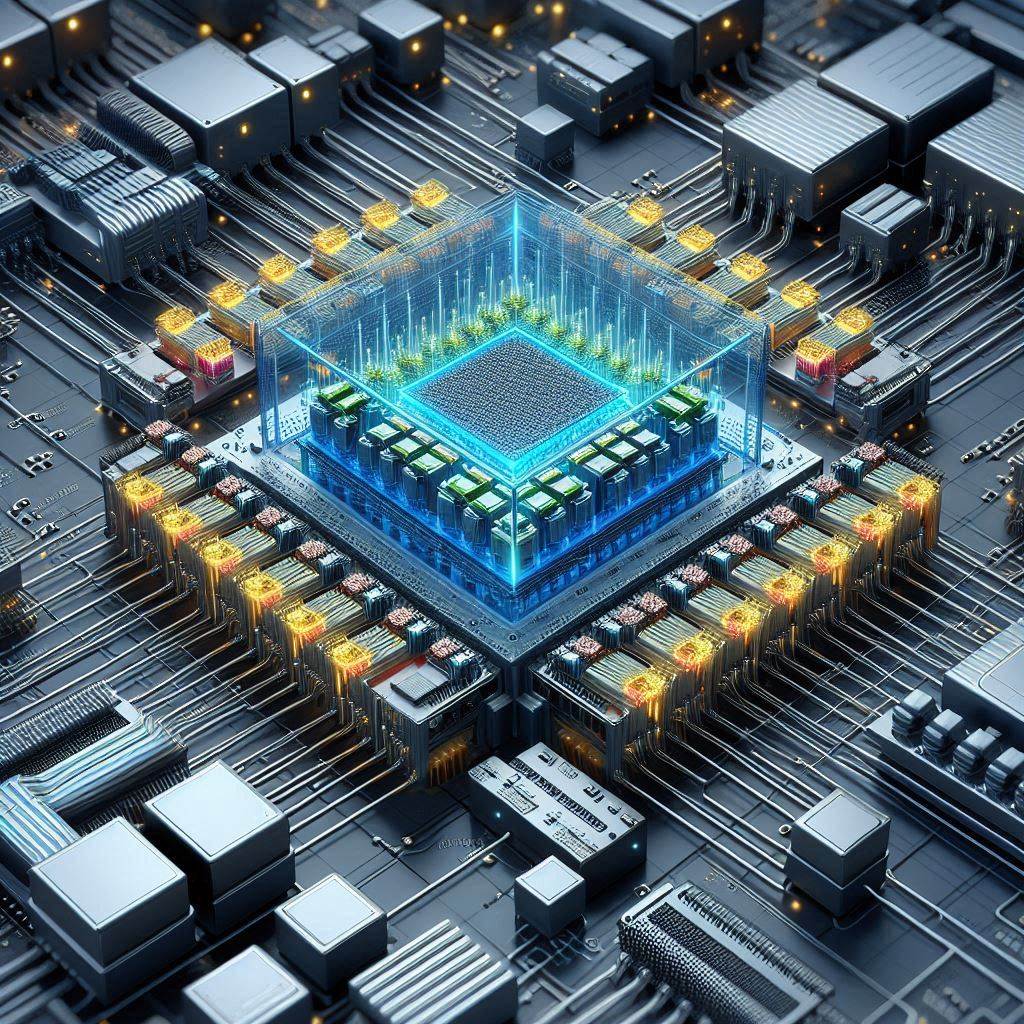

Interconnect and bitcell optimization for 3D heterogeneous embedded cache systems

Leuven | More than two weeks ago

Optimizing Interconnects and Bitcells for Next-Gen 3D Embedded Cache Systems: Powering the Future of High-Density, Energy-Efficient Memory

Over the decades, CMOS technology has enabled aggressive scaling of computing systems, primarily in an inward direction, resulting in increasingly smaller systems. However, as we progress, this inward scaling yields diminishing returns. Embedded caches based solely on SRAMs do not scale inwardly, occupying a growing area relative to the size of logic cores/multicores. As logic continues to shrink, the number of cores on a system has multiplied in recent years, necessitating larger amounts of embedded memory. How can we power or clock such embedded systems in the most energy-efficient way?

In addition to geometric constraints, state-of-the-art system functionality is increasingly driven by data-intensive applications like AI and ML, which demand higher memory capacities and advanced memory management schemes both within and beyond the chip. Edge devices, on the other hand, prioritize energy efficiency to extend battery life. Key limiting factors such as system yield, testing, dynamic and static power, data integrity, and variability hinder continued scaling at the current level. However, due to these growing demands, system expansion is still necessary, primarily occurring in an outward direction.

One decisive technological direction is the 3D integration of heterogeneous technologies, sometimes referred to as 5.5D integration. However, larger, deeper, denser embedded caches and the data movement to off-chip 2.5D memory systems entail issues primarily related to interconnects such as power, clock, and signal, which must be solved to achieve higher energy efficiency. Our approach needs to focus primarily on interconnect issues rather than device issues.

The general research domain of this work is the integration of power, clock, and signal delivery to 3D embedded cache memories, building upon the existing SRAM and mixed-signal knowledge base. The key outputs of this research work are:

- Design enablement of a 5.5D system: Solving issues of power and signal delivery to and from embedded caches to logic. This includes handling multiple power or clock domains, asynchronous clocking, or resonant clocking across multiple tiers. It may involve integrating a multi-layer power delivery/gating system based on tightly integrated deep-trench MiM-Caps or distributed LDOs for delivering power to multiple, simultaneous switching MRAM bit-cells. Assessing the impact of interconnect choices such as TSVs or hybrid bonding is also crucial.

- Mixed-signal or physical design of a cache memory circuit: Enabling multi-tier compute in multi-port/pumped memory within a logic-memory co-optimization framework. This involves automatic synthesis and place-and-route for co-optimizing key parameters such as energy, power, access latency, crosstalk, yield, and test. Achieving maximum energy efficiency through the physical design process is a key output.

- Interdisciplinary and technology-intensive exploration: Investigating 3D cache memory in the context of the heterogeneity of the technology involved. This heterogeneity can degrade the energy efficiency achieved via the first two aspects. This involves modeling suitable device ecosystems based on new materials/process steps, including variability analysis and temperature analyses of hybrid CMOS-NV 6T-12T bitcells or different materials. The choice of the right dielectric material or a thermal spreader can make a significant difference. Sensor integration is another direction to explore. This interdisciplinary area will involve collaboration among relevant disciplines and other PhDs.

Required background: Electrical Engineering

Type of work: 50% mixed signal circuit design, 20% modeling, 20% literature survey and 10% publication.

Supervisor:

Daily advisor: Prashant Dubey

The reference code for this position is 2025-069. Mention this reference code on your application form.