Autonomous edge chiplet program

Chiplet architectures will drive high-performance computing in autonomous edge systems. Imec and its partners prepare this shift through reference architectures and physical testbeds.

High-performance computing (HPC) is no longer confined to data centers. It must increasingly operate at the edge, close to data generation and real-time decision-making. Any system that acts in a complex, unpredictable environment will need significant local compute to take correct and safe decisions.

Such elevated compute cannot solely run on chips that rely on monolithic IC design.

One of the first application domains where this was realized is automotive. The compute performance needed to drive next-generation ADAS/AD and in-vehicle infotainment (IVI) is immense. Soon, every car will need a supercomputer on board. Chiplet architectures, combining chips designed to perform specific functions efficiently, will allow car OEMs to aim for cost-effective systems tailored to the demands of various applications. And quickly adapt those systems across car models and model generations by swapping chiplets, not unlike LEGO blocks.

Why are chiplets attracting the attention of the automotive industry?

Paving the way for autonomous edge chiplets

Chiplets are already used in high-performance computing, servers and consumer devices. However, the higher quality and reliability (QnR) requirements in the automotive industry elevate complexity and necessitate novel solutions from the architecture down to the level of materials. Furthermore, an open automotive chiplet ecosystem with a high level of interface standardization and agreed-upon architecture blueprints across the industry is imperative to ensure interoperability, compatibility, and scalability – resulting in more flexibility regarding chip architectures and a reduced time-to-market for OEMs.

This equally applies to sectors that have similar requirements around performance, determinism, safety and resilience:

- robotics with embedded AI

- smart infrastructure and energy systems

- aerospace, defense, and secure communication

Imec plays a leading role in standardization efforts by bringing together leading players from the automotive industry players to align in the Automotive Chiplet Forum.

At the same time, the autonomous edge chiplet program aims at accelerating and derisking chiplet adoption for contributing partners through pre-competitive research that leverages imec’s infrastructure and expertise.

This research program comprises two tracks: the investigation of interconnect QnR and the development of a reference architecture.

AECP Partners

In 2024, imec announced the first partners of its automotive chiplet program, the predecessor of the autonomous edge chiplet program.

Currently, the program brings together 22 partners: Arm, Audi, BMW Group, Bosch, Cadence, Cariad, GlobalFoundries, Infineon, LG Electronics, L&T Technology Services, MIPS, Porsche, Rivian, Siemens, SiliconAuto, Silicon Box, STATS ChipPAC, Synopsys, Tenstorrent, TIER IV, Valeo, and Volkswagen.

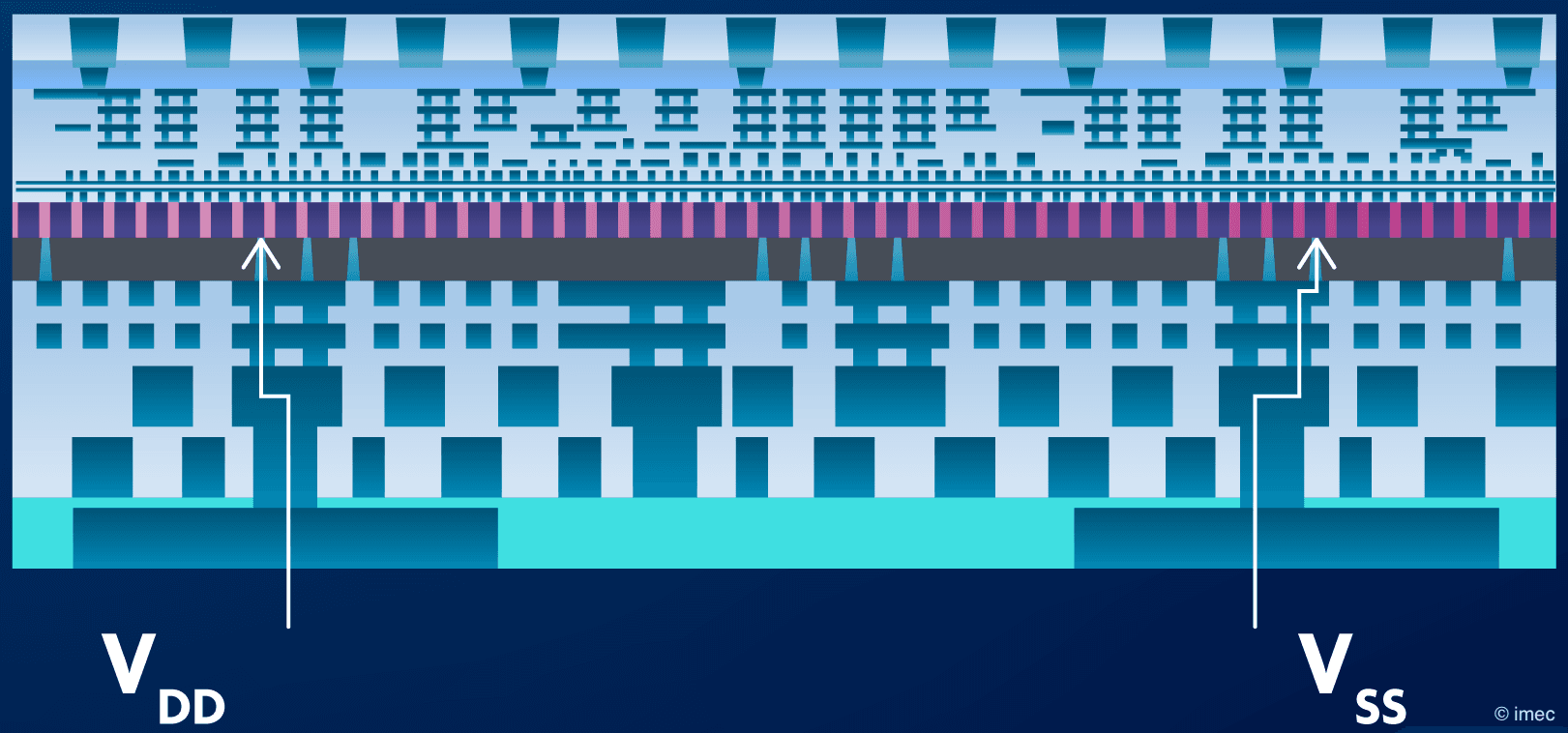

Track 1: reference architectures

The first step is to develop digital models of chiplet architectures geared to the system-level needs of autonomous edge solutions. These reference architectures will be used to create physical models in track 2, and they offer valuable insights for early software development.

Track 2: interconnect QnR

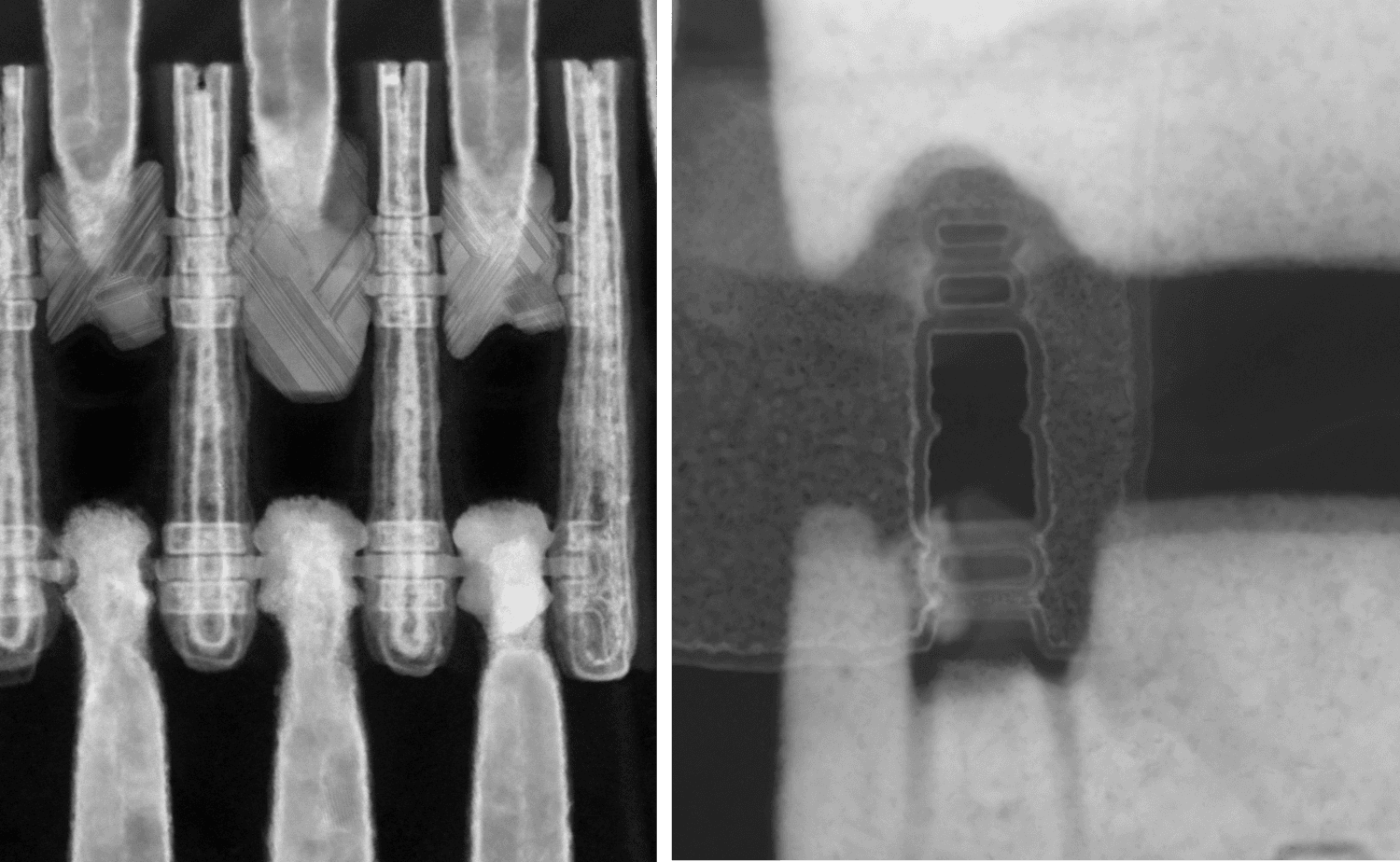

Which chiplet interconnect technologies will meet the most stringent requirements regarding temperature cycles, vibrations, and so on (e.g. AEC-Q100 grade 2 at 10 DRM)? Imec’s autonomous edge chiplet program tackles this question by building physical test structures inspired by the research from track 1 and based on the PTCQ chips developed in imec’s 3D integration research program.

These thermo-mechanical testbeds mimic real physical architectures and internal thermal load conditions, and allow e.g. ACQ-100 testing. The resulting insights into the most appropriate interconnect technologies for autonomous edge chiplets will be shared with all program partners.

Work with us

Imec’s precompetitive autonomous edge chiplet program is geared to a wide range of actors in the ecosystem, from OEMs, foundries and IDMs to chiplet vendors. By tapping into imec’s unparalleled expertise in semiconductor scaling, 3D integration, and HPC modeling, all partners lay the groundwork for a rapid, de-risked adoption of chiplets in their future products.

In bilateral projects, imec is also ready to bridge the results from our R&D program towards the next step, which is to productize a specific chiplet-based solution through IC-Link.

Want to join imec’s autonomous edge chiplet program or talk about your high-performance computing challenge?

Click the button below to get in touch.

This research is partially funded by the State of Michigan.